Сменными составными элементами панели являются:

| Ячейка MPS |

1 шт. |

| Модуль памяти DDR2 2GB KVR400D2D8R3/2G фирма Kingston |

8 шт. |

| Модуль Ethernet 10/100 PCI 3C-905C фирма 3COM |

1 шт. |

| Модуль графического контроллера PCI Rage Pro 16Mb фирма ATI Technologies |

1 шт. |

| Звуковая карта PCI Crystal SemiconductorsCS4281-СQ фирма Chipset |

1 шт. |

| Модуль SCSI-2 PCI AHA-2940 фирма Adaptec |

1 шт. |

Модули памяти DDR2устанавливаются в соединители socket DDR DIMM 240CKTS фирмы MOLEX (X12…X17, X19, X20). Модули PCI – в соединители socket PCI фирмы AMP (Х42, Х45, Х48, Х52).

Структурная схема системной панели ПЭ3М1

CPU – микропроцессор «Эльбрус»; SCU – системный контроллер; DCU – коммутатор данных; MC – контроллер памяти; I/O– системный контроллер ввода-вывода («северный мост»); SB – периферийный контроллер ввода-вывода («южный мост»); SUPER I/O – контроллер последовательно-параллельных интерфейсов и Floppy; I/O PIC – контроллер прерываний ввода-вывода; TL PIC – двойной локальный контроллер прерываний; ППЗУ Boot – загрузочное программируемое постоянное запоминающее устройство; ППЗУ BIOS – программируемое постоянное запоминающее устройство системного программного обеспечения.

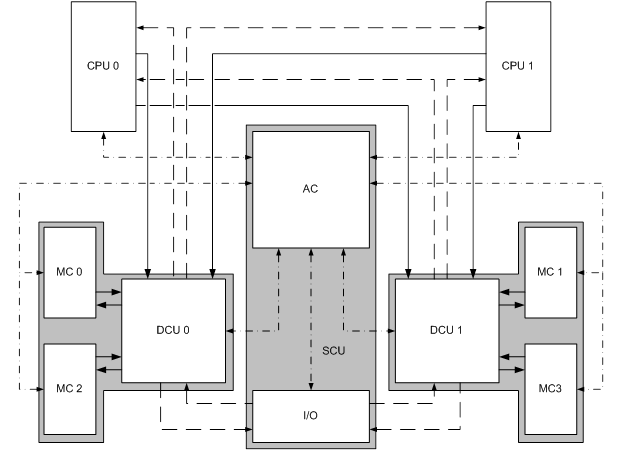

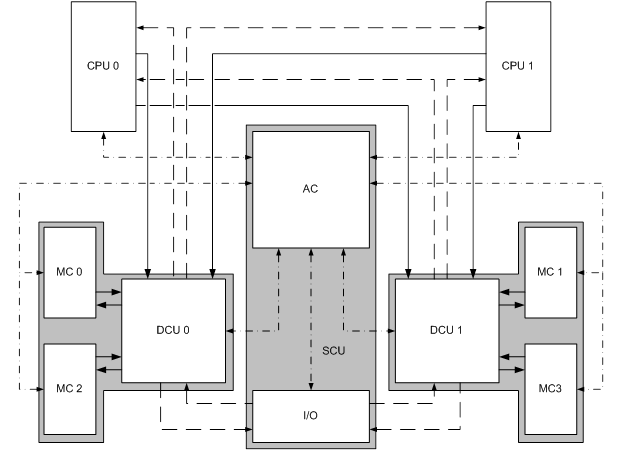

Структурная схема центральной части ПЭ3М1

CPU – микропроцессор «Эльбрус»; DCU – коммутатор данных; AC – коммутатор адреса; MC – контроллер памяти; I/O – системный контроллер ввода/вывода («северный мост»); SCU – системный контроллер.

Коротко рассмотрим назначение основных элементов материнской платы ПЭ3М1.

Коммутатор адреса AC направляет заявки (адреса) от двух процессоров (CPU0 и CPU1) либо в контроллер памяти для доступа к секциям оперативной памяти DIMM, либо в «северный мост» для доступа к устройствам ввода-вывода. Кроме того, проверяет наличие копий данных, к которым идут обращения, в кэш-памяти процессоров и реализует протокол когерентности, т.е. поддержки соответствия состояний этих копий друг другу и содержимому памяти.

Системный контроллер ввода-вывода (В/В) I/O («северный мост») разделяет заявки, направленные к шинам LVDS и PCI. Кроме того, к функциям «северного моста» относятся:

- формирование сигналов начальной установки системы;

- организация «раскрутки» миниОС «Эльбрус»;

- сбор прерываний и переадресация их процессорам (для этого в «северном мосте» размещены два локальных программируемых контроллера прерываний с расширенными возможностями TL PIC, по числу процессоров в системе);

- организация обращений к внутренним регистрам Chipset.

Системный контроллер В/В со стороны центральной системы взаимодействует с адресным коммутатором AС и коммутатором данных DCU. Интерфейс с коммутатором AS служит для приёма и выдачи заявок на выполнение транзакций, интерфейс с коммутатором DS обслуживает приём/выдачу данных. Поддерживает интерфейс шины PCI, соответствующий PCI Local Bus Specification, Revision 2.2 и интерфейс шины LVDS.

Коммутатор адреса и контроллер ввода/вывода располагаются в одной ПЛИС, образующей системный контроллер SCU. Аналогичное объединяются коммутаторы данных и соответствующие контроллеры памяти (МС).

Коммутатор данных DCU служит для передачи данных между центральными процессорами CPU0, CPU1, контроллерами памяти MC и «северным мостом».

Контроллер памяти MC, встроенный в адресный коммутатор, реализует адресный интерфейс с секциями накопителя, построенного на базе DIMM DDR SDRAM модулей.

Коммутатор данных DS связывает DIMM DDR SDRAM модули с процессорами и с «северным мостом». Все линии связи в процессорном модуле, за исключением связей DIMM DDR SDRAM модулей с коммутатором данных, однонаправленные.

В качестве периферийного контроллера ввода-вывода I/O SB («южного моста») используется покупной контроллер PIIX4, входящий в chipset 440GX фирмы Intel.

PCI (Peripheral Component Interconnect) local bus – шина соединения периферийных компонентов. Представляет собой 32-разрядную шину с тактовой частотой 33 МГц и пропускной способностью до 132 Мбайт/с.

LVDS (Low Voltage Differential Signals) – высокоскоростная шина ввода-вывода, состоящая из 24 однонаправленных дифференциальных пар, 12 из которых работают на приём, 12 на выдачу данных. Данная шина может работать на частоте до 655 МГц, что обеспечивает пропускную способность до 980 Мбайт/с в каждую сторону. Подключается эта шина через стандартный слот AGP.