Модуль процессорных ядер МПЯ2 - высокопроизводительный вычислитель на базе Системы на кристалле МЦСТ R500S (1891ВМ3Я). Выполнен на основе стандарта ETX компонентов SBC ст. 2.7 фирмы Kontron .

Модуль процессорных ядер МПЯ2 - высокопроизводительный вычислитель на базе Системы на кристалле МЦСТ R500S (1891ВМ3Я). Выполнен на основе стандарта ETX компонентов SBC ст. 2.7 фирмы Kontron .

Модуль процессорных ядер МПЯ2 - высокопроизводительный вычислитель на базе Системы на кристалле МЦСТ R500S (1891ВМ3Я). Выполнен на основе стандарта ETX компонентов SBC V 2.7 фирмы Kontron.

Основной элемент модуля - многослойная печатная плата с установленными на ней интегральными микросхемами, соединителями и передней панелью.

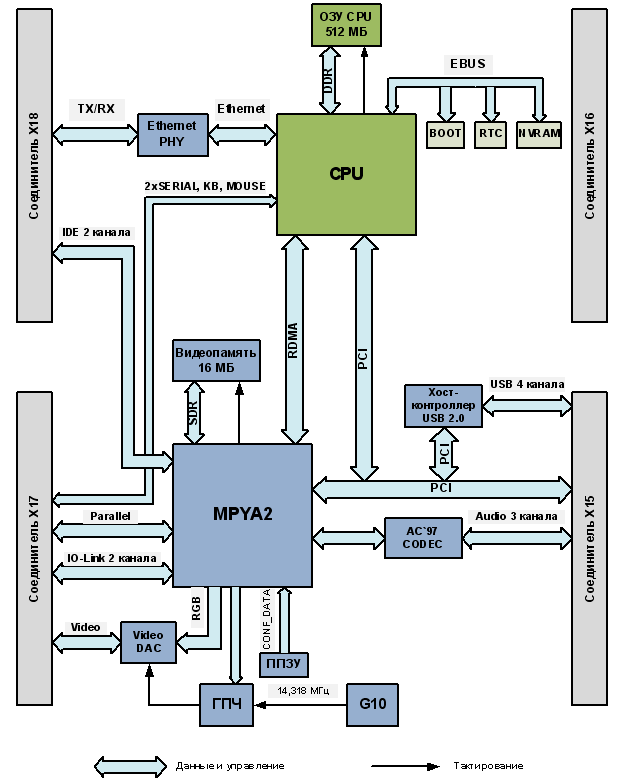

Микропроцессор МЦСТ R500 S (1891ВМ3Я) - основной узел модуля. Выполнен на основе архитектуры с сокращённым набором команд - RISC. Отвечает за выполнение арифметических, логических операций и операций управления в машинных кодах. Для соединения процессора с контроллером MPYA2 используются 32-разрядная (33 МГц) шина PCI и дуплексный канал удалённого доступа RDMA.

Контроллер MPYA2 содержит внутренние контроллеры памяти, параллельного порта, IDE, видео, аудио. Контроллер подключён к:

С контроллера выходит шина PCI, к которой подключены:

К периферийной шине EBUS подсоединяются:

| Параметр | Значение |

|---|---|

| Микропроцессор | 1 × МЦСТ R 500 S |

| Тактовая частота процессора, МГц | 400 |

| Кэш команд процессора, Кбайт | 16 |

| Кэш данных процессора, Кбайт | 32 |

| Кэш второго уровня процессора, Кбайт | 512 |

| Оперативная память, Мбайт | 512 |

| Видеопамять, Мбайт | 16 |

| Каналы ввода / вывода | RDMA, Ethernet, RS-232, SCSI-2, аудио, видео, PS / 2 |

| Средняя наработка на отказ ВК, ч, не менее | 9000 |

| Группа исполнения | 1.10 (в ВК НТ R500S) |

| Потребляемая мощность, Вт | 6 |

| Диапазон рабочих температур внешних условий применения, ° С | -30 ... + 55 (в ВК НТ R500S) |

| Год начала производства | 2010 |

В состав модуля МПЯ2 выходят:

Поддерживается стандартный комплект программного обеспечения для платформы SPARC .