Основные составные части ячейки МОП

- соединитель SBus-шины;

- контроллер обработки прерываний KOP;

- контроллер приёма прерываний PPR;

- постоянное запоминающее устройство ПЗУ;

- приёмник прерываний (3 микросхемы 1533ЛН1);

- передатчик прерываний (4 микросхемы 1533ЛИ1);

- соединитель JP1-JP5 подключения разъёма JTAG;

- соединитель JP6-JP12 установки прерывания SBus-шины с помощью перемычки;

- микросхема синхронизации;

- микропроцессор S80C186EC13 фирмы Intel (13 МГц);

- внешний соединитель интерфейса прерываний.

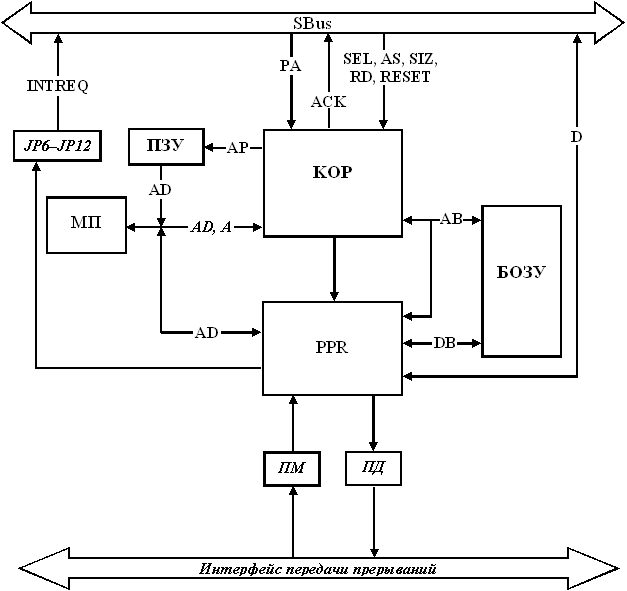

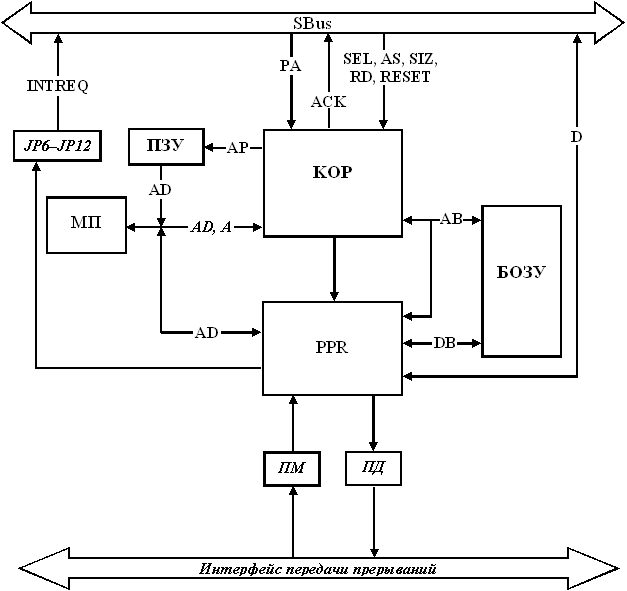

Структура ячейки МОП

KOP – контроллер обработки прерываний;

PPR – контроллер приёма прерываний;

МП – микропроцессор S80C186EC13;

ПЗУ – программируемая постоянная память AT29C1024 (64 Кбайт × 16);

БОЗУ – буферная память (2 × 32 Кбайт × 9);

ПМ– приёмник прерываний;

ПД– передатчик прерываний;

DB – 18-разрядная внутренняя шина DВ[15:0], DBP[1:0];

D – 16-разрядная шина данных D[31:16];

AD – 16-разрядная шина МП AD[15:0];

A – 3-разрядная шина МП A[19,18,16];

AB – 15-разрядныя шина адреса БОЗУ AB[14:0];

AР – 16-разрядная шина ПЗУ AP[15:0].