Арт. ТВГИ 469535.067

Ячейка ММР/М предназначена для обмена информацией между оперативной памятью процессорного модуля и внешними абонентами по каналу обмена «Манчестер-2».

Арт. ТВГИ 469535.067

Ячейка ММР/М предназначена для обмена информацией между оперативной памятью процессорного модуля и внешними абонентами по каналу обмена «Манчестер-2».

Ячейка ММР/М представляет собой ячейку в конструктиве РМС, устанавливаемую в модуль с помощью соединителя мезонина РМС, имеющая 2 канала ввода-вывода (0К – основной, 1К – резервный), с темпом обмена - 1 Мбит/с и возможным удалением – 100 м.

Ячейка ММР/М предназначена для обмена информацией между оперативной памятью процессорного модуля в режиме прямого доступа в память (ПДП) по шине ввода/вывода типа PCI и каналом обмена, по стандарту «Интерфейс магистральный последовательный системы электронных модулей ГОСТ 26765.52-87» (Манчестер-2).

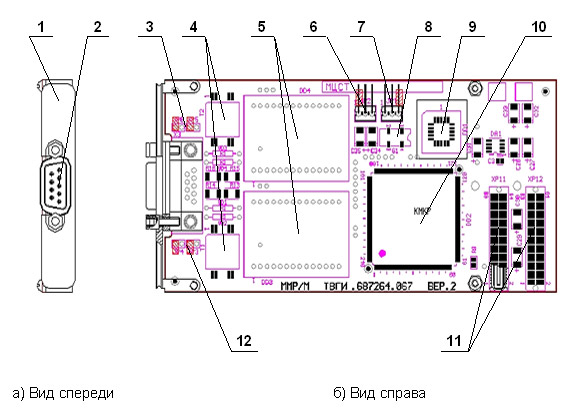

1 – передняя панель ячейки; 2 – разъем последовательного интерфейса; 4 – трансформатор ТИЛ5В; 5 – микросборка ВА996А1 (приемопередатчик); 8 – осциллятор SG-8002JC (генератор 24 МГц); 9 – микросхема ППЗУ EPC2LC20; 10 – микросхема ПЛИС КМКР EP1C6Q240C8; 11 – разъем интерфейса PCI.

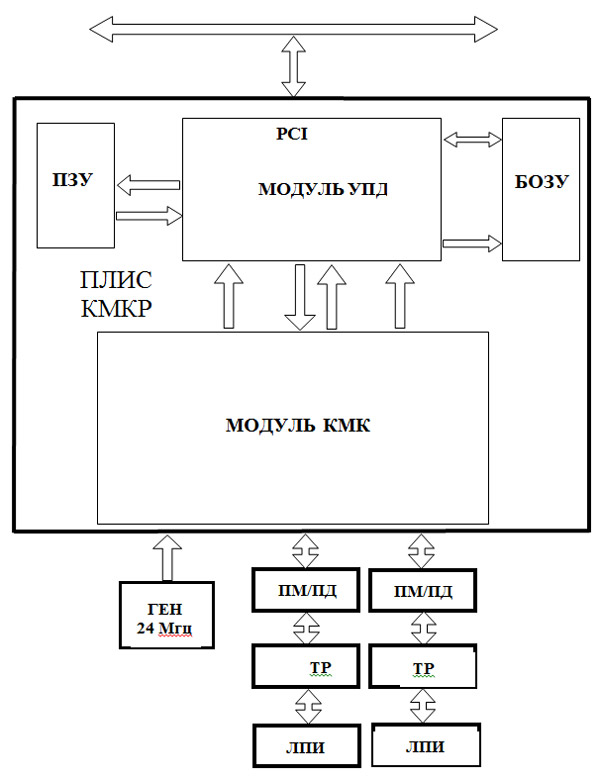

Блок схема ячейки ММР/М:

Шина PCI

ПЛИС КМКР - контроллер мультиплексного канала с контроллером PCI; ГЕН - Генератор тактовой частоты 24 МГц; ПМ/ПД - приемопередатчик - микросборка ВА996А1; ТР - трансформатор ТИЛ5В; ЛПИ - линия передачи информации (КВСФ-75).

Схема ячейки ММР/М состоит из модуля УПД, обеспечивающего обмен информацией между оперативной памятью процессорного модуля и буферной оперативной памятью (БОЗУ) модуля в режиме ПДП по шине PCI, и модуля контроллера манчестерского кода (КМК), выполняющего функции «контроллера», «оконечного устройства» в соответствии с ГОСТ 26765.52-87.