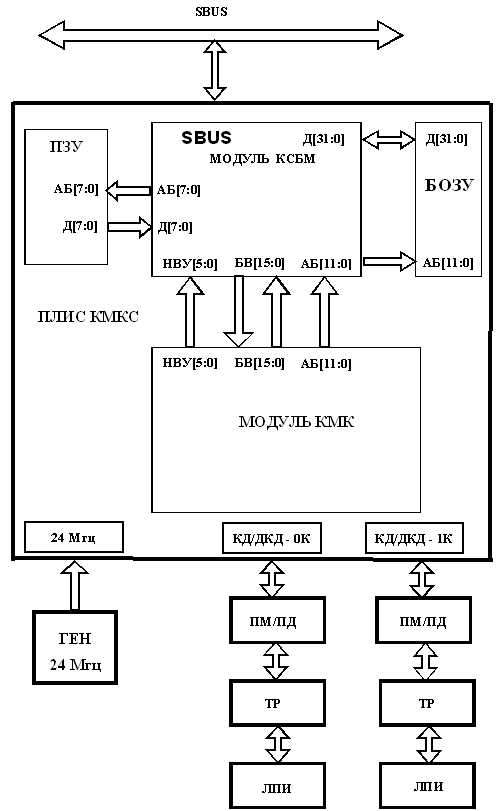

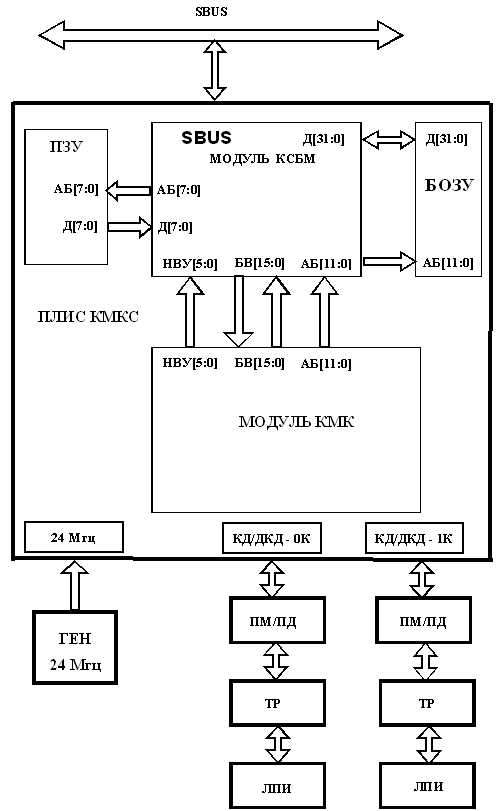

Структура ячейки ММР

- ПЛИС КМКС – контроллер мультиплексного канала с контроллером SBus.

- ГЕН – генератор тактовой частоты 24 МГц.

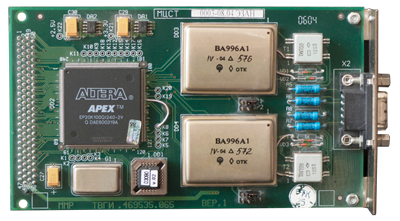

- ПМ/ПД – приёмопередатчик – БИС ВА996А1.

- ТР – трансформатор ТИЛ5В.

- ЛПИ – линия передачи информации КВСФ-75.

Контроллер мультиплексного канала с контроллером КМКС включает в себя:

- модуль КСБМ, обеспечивающего обмен информацией между оперативной памятью устройства УВ 3М1 и буферной ОП КМКС в режиме ПДП по шине SBus;

- буферную оперативную память (БОЗУ);

- модуль контроллера манчестерского кода (КМК), выполняющего функции «контроллера», «оконечного устройства» или «монитора» в соответствии с ГОСТ 26765.52-87;

- постоянное запоминающее устройство (ПЗУ), для хранения системной информации об ячейке ММР.

Модуль КСБМ состоит из трёх основных узлов:

1) Контроллер системной шины, который обеспечивает режимы «задатчик» и «исполнитель» в соответствии с протоколом шины SBus для обмена информацией между ОП устройства УВ 3М1 и БОЗУ ПЛИС КМКС в режиме ПДП, для чтения системной информации из ПЗУ, для записи и чтения информации в/из программно доступных регистров.

2) Модуль управления ПДП ПЛИС КМКС (УПДМ), который обеспечивает обмен информацией между модулем КМК и соответствующими буферами в памяти ПЛИС КМКС и формирует запросы для БОЗУ на обмен с буферами программы пользователя через системную шину.

3) Блок программно доступных регистров (РОБ).

В буферной оперативной памяти (БОЗУ) реализованы следующие режимы работы по системной шине:

- исполнитель – запись/чтение;

- задатчик – запись/чтение.

Модуль управления прямым доступом к БОЗУ (УПДМ) обеспечивает:

- Обмены КМК с соответствующим буфером БОЗУ по запросу из КМК; при этом обеспечивается считывание, модификация и запись управляющей информации буфера.

- Инициализацию запросов в БОЗУ для обращения к SBus шине при исчерпании или наполнении очередного полубуфера, с которым производится обмен.

- Инициализацию запросов в БОЗУ для обращения к SBus шине при подкачке информации в буфер команд КМК и откачке результатов выполнения команд.

Постоянное запоминающее устройство ПЗУ доступно только по чтению и содержит информацию, которая используется операционной системой УВС для определения типа ячейки, занимающей некоторый слот системной шины, и подключения к ней соответствующего драйвера. ПЗУ инициализируется информацией из специального файла при программировании ПЛИС КМКС

Режимы работы ячейки ММР:

- режим «контроллер»;

- режим «оконечное устройство»;

- режим «монитор».

Контроллер манчестерского кода КМК состоит из следующих основных узлов:

- Кодер. Преобразует параллельный код информации в последовательный биполярный код. Сигналы последовательного биполярного кода имеют уровень «ТТЛ» и поступают в приёмопередатчик ВА996А1 для преобразования сигналов уровня «ТТЛ» в сигналы уровня определённого ГОСТ 26765.52-87, а затем через развязывающий трансформатор передаются в ЛПИ.

- Декодер. КМК имеет два декодера, по одному на каждый канал. На приёме информация из ЛПИ через развязывающий трансформатор поступает в приёмопередатчик ВА996А1 для преобразования сигналов уровня определённого ГОСТ 26765.52-87 в сигналы уровня «ТТЛ». Сигналы последовательного биполярного кода уровня «ТТЛ» поступают на вход соответствующего декодера и преобразуются в параллельный код, при этом производится анализ входных сигналов в соответствии с ГОСТ 26765.52-87.

- Блок управления предназначен для работы с соответствующими буферами для приёма или передачи информации, а также для работы с буфером команд и статистики.