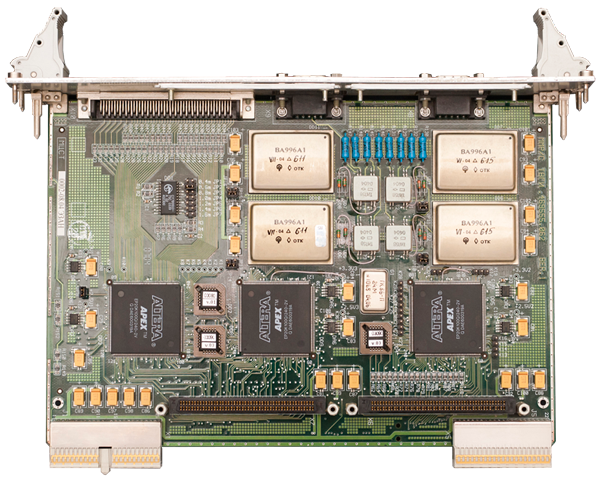

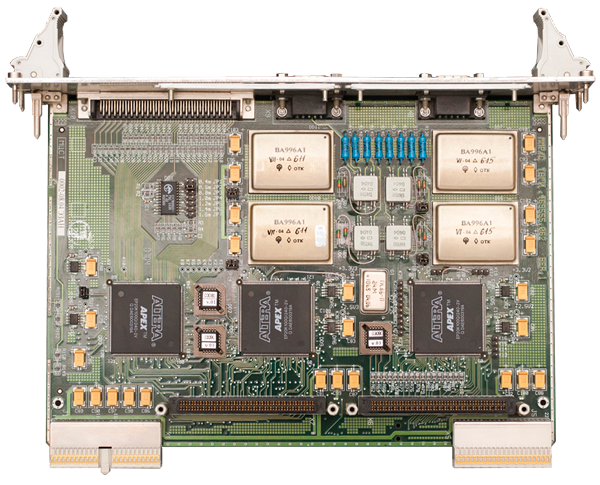

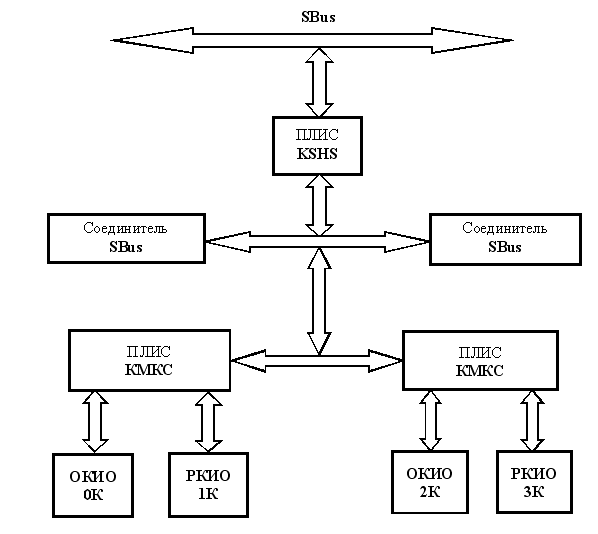

В состав модуля ММР/С входят:

- Контроллер мультиплексного канала с контроллером SBus – ПЛИС КМКС.

- Контроллер системной шины SBus – ПЛИС KSHS.

- Основной канал информационного обмена – ОКИО.

- Резервный канал информационного обмена – РКИО.

- Генератор тактовой частоты 24 МГц – ГЕН.

- Приёмопередатчик основного канала – БИС ВА996А1 – ПМ/ПД.

- Трансформатор основного канала – ТИЛ5В – ТР.

- Линия передачи информации (КВСФ-75) основного канала – ЛПИ.

- Приёмопередатчик резервного канала – БИС ВА996А1 – ПМ/ПД.

- Трансформатор резервного канала – ТИЛ5В – ТР.

- Линия передачи информации (КВСФ-75) резервного канала – ЛПИ.

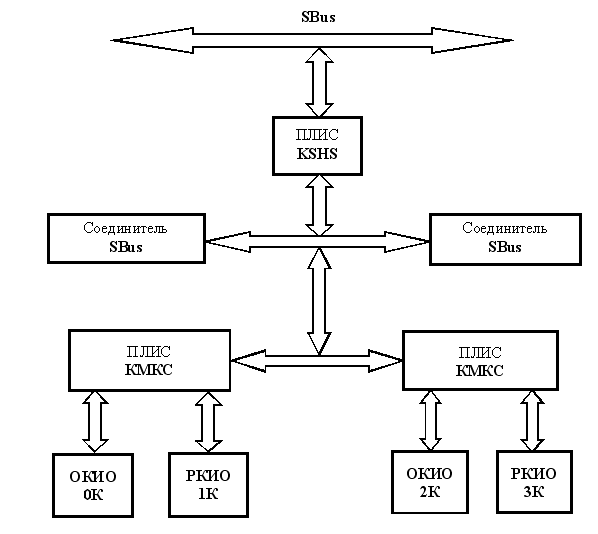

Структура модуля ММР/С

Контроллер SBus-шины KSHS представляет собой программируемую логическую интегральную схему (ПЛИС). Осуществляет передачу команд с шины одного уровня на шину другого. Для шины, из которой идёт передача, контроллер является исполнителем. Для шины, в которую идёт передача, контроллер является задатчиком. Будучи задатчиком, контроллер KSHS может получить уведомление об ошибке. В случае выполнения команды записи контроллер, получив такое уведомление, завершает выполнение текущей команды и аппаратура приводится в состояние готовности к выполнению следующей команды. В этой ситуации формирование прерывания возлагается на исполнителя. Если контроллер получает уведомление об ошибке, являясь задатчиком команды чтения, он, завершив выполнение текущей команды для вторичной шины, ожидает повторного запроса от задатчика первичной шины и выдаёт ему уведомление об ошибке, сообщая о неблагополучном завершении команды.

Адресное пространство самого контроллера всегда начинается с нулевого адреса. Для виртуального режима его размер составляет 1 Мбайт, при физическом режиме контроллеру KSHS отводится стандартная 1/8 часть (как и абонентам).

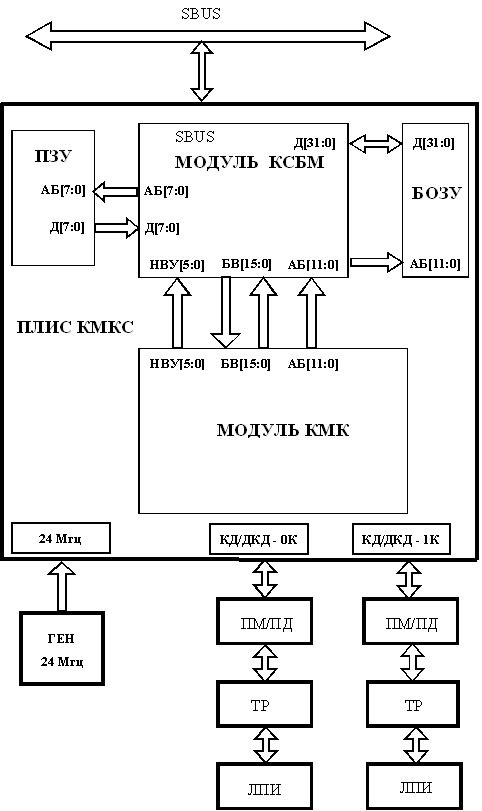

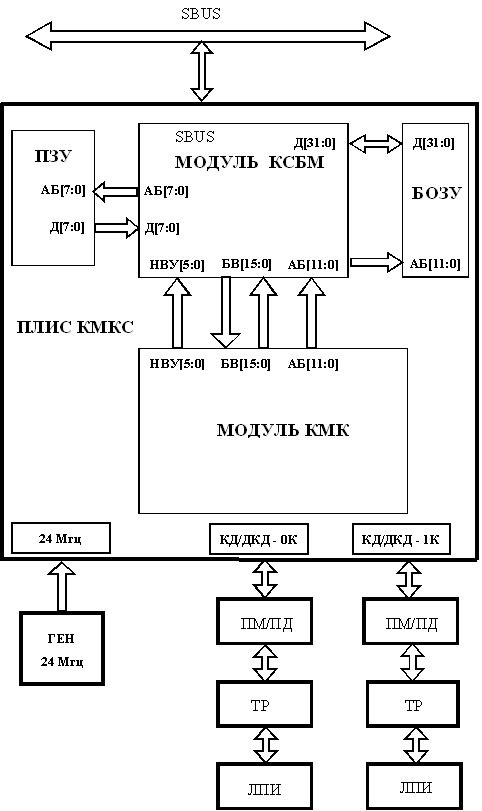

Структура ПЛИС КМКС и каналов информационного обмена.

Схема КМКС включает в себя модуль КСБМ, буферную оперативную память (БОЗУ), модуль контроллера манчестерского кода (КМК), постоянное запоминающее устройство (ПЗУ), для хранения системной информации о ячейке ММР.

Модуль КСБМ обеспечивает обмен информацией между ОП модуля МV/С и буферной ОП ПЛИС КМКС в режиме ПДП по шине SBus.

Модуль КСБМ состоит из трёх основных узлов:

- Контроллер системной шины. Обеспечивает режимы «задатчик» и «исполнитель» в соответствии с протоколом шины SBus для обмена информацией между ОП МV/С и БОЗУ ПЛИС КМКС в режиме ПДП, для чтения системной информации из ПЗУ, для записи и чтения информации в/из программно доступных регистров.

- Модуль управления прямым доступом в память ПЛИС КМКС. Обеспечивает обмен информацией между модулем КМК и соответствующими буферами в памяти ПЛИС КМКС. Формирует запросы для БОЗУ на обмен с буферами программы пользователя через системную шину.

- Блок программно доступных регистров (РОБ).

Модуль буферной оперативной памяти (БОЗУ) реализует следующие режимы работы по системной шине:

а) Исполнитель – запись/чтение.

Режим работы «исполнитель» – запись/чтение запускается по инициативе арбитра SBus-шины выдачей сигнала селекции в ячейку ММР, который поступает в узел БОЗУ. В ответ БОЗУ запускает обмен в соответствии с протоколом SBus-шины. В режиме «исполнитель» программа пользователя через драйвер ячейки ММР может иметь доступ к БОЗУ, ПЗУ или РОБ ПЛИС КМКС.

б) Задатчик – запись/чтение.

Режим работы задатчик – запись/чтение запускается от запроса УПДМ на откачку или подкачку информации из или в буфер обмена. БОЗУ выдаёт в арбитр SBus-шины требование для доступа к шине для обмена информацией. Арбитр SBus-шины в ответ на это требование выдаёт сигнал разрешения на обмен, после чего БОЗУ запускает обмен в соответствии с протоколом шины.

Модуль управления прямым доступом к БОЗУ (УПДМ) обеспечивает:

- Обмены КМК с соответствующим буфером БОЗУ по запросу из КМК. При этом обеспечивается считывание, модификация и запись управляющей информации данного буфера.

- Инициализацию запросов в БОЗУ для обращения к SBus-шине при исчерпании или наполнении очередного полубуфера, с которым производится обмен.

- Инициализацию запросов в БОЗУ для обращения к SBus-шине при подкачке информации в буфер команд КМК и откачке результатов выполнения команд.

Постоянное запоминающее устройство (ПЗУ) доступно только по чтению и содержит информацию, которая используется операционной системой ВК для определения типа ячейки, занимающей некоторый слот системной шины, и подключения к ней соответствующего драйвера. ПЗУ инициализируется информацией из специального файла при программировании ПЛИС КМКС.

Контроллер манчестерского кода (КМК) выполняет функции «контроллера», «оконечного устройства» или «монитора» в соответствии с ГОСТ 26765.52-87. Состоит из следующих основных узлов

- Кодер преобразует параллельный код информации в последовательный биполярный код. Сигналы последовательного биполярного кода уровня «ТТЛ» поступают в приёмопередатчик ВА996А1 для преобразования сигналов уровня «ТТЛ» в сигналы уровня по ГОСТ 26765.52-87, а затем через развязывающий трансформатор передаются в ЛПИ. Для выдачи кода используется соответствующий канал МКИО.

- Декодер. КМК имеет два декодера, по одному на каждый канал. На приёме информация из ЛПИ через развязывающий трансформатор поступает в приёмопередатчик ВА996А1 для преобразования сигналов уровня по ГОСТ 26765.52-87 в сигналы уровня «ТТЛ». Сигналы последовательного биполярного кода уровня «ТТЛ» поступают на вход соответствующего декодера и преобразуются в параллельный код.

- Блок управления предназначен для работы с соответствующими буферами для приёма или передачи информации, а также для работы с буфером команд и статистики.