Ячейка модуля стандартного канала МСКК предназначена для связи между вычислительным комплексом (ВК) и вводом/выводом ЕС ЭВМ-канал. Представляет собой однослотовую SВus-ячейку с двумя соединителями.

Ячейка модуля стандартного канала МСКК предназначена для связи между вычислительным комплексом (ВК) и вводом/выводом ЕС ЭВМ-канал. Представляет собой однослотовую SВus-ячейку с двумя соединителями.

Ячейка модуля стандартного канала МСКК предназначена для связи между вычислительным комплексом (ВК) и вводом/выводом ЕС ЭВМ-канал. Представляет собой однослотовую SВus-ячейку с двумя соединителями.

Основные характеристики ячейки МСКК

| Параметр | Значение |

| Интерфейс | шина SBus. |

| Средняя наработка на отказ ВК, ч, не менее | 9000 |

| Группа исполнения | зависит от ВК |

| Потребляемая мощность, Вт | 6 |

| Диапазон рабочих температур внешних условий применения, °С | зависит от ВК |

| Год начала производства | 2005 |

Основные составные части ячейки МСКК

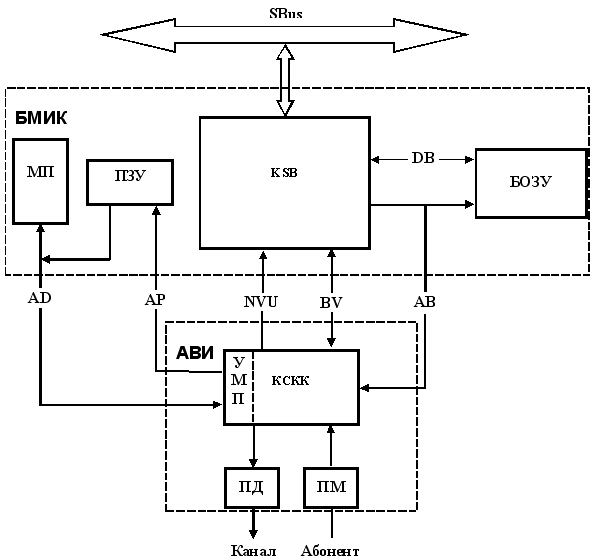

Структура ячейки МСКК

Взаимодействие составных частей ячейки МСКК обеспечивается связями:

- DВ – 36-разрядная внутренняя шина

- BV – 18-разрядная внутренняя шина данных

- AD – 19-разрядная шина МП

- AB – 15-разрядный адрес БОЗУ

- AР – 16-разрядная шина ПЗУ

- NVU – 4-разрядный номер внешнего устройства

Ячейка МСКК состоит из двух основных узлов:

Базовый микроконтроллер (БМИК) является основным вычислительным средством контроллеров внешних интерфейсов (КВИ) и реализован с использованием микропроцессора S80C186EC-13 с тактовой частотой 13 МГц. В узел БМИК входят:

Основные функции БМИК:

ПЛИС KSB совмещает в себе функции контроллера системной шины SВus и контроллера БОЗУ.

Адаптер внешних интерфейсов (АВИ) предназначен для обмена информацией между БМИК и каналом ввода/вывода ЕС ЭВМ.

ВАВИ входят:

ПЛИС контроллера стандартного канала и микропроцессора (КСКК) является адаптером внешних интерфейсов и стандартным образом через устройство управления микропроцессором (УМП) подключается к шине AD микропроцессора и шине BV буферной памяти. КСКК реализует канал, работающий в режиме блок-мультиплексной и байт-мультиплексной передачи данных. Реализация канала осуществлена по принципу программно-аппаратного управления с использованием БМИК. В КСКК входят следующие узлы:

Поддерживается стандартный комплект программного обеспечения для платформы «Эльбрус».