Ячейка модуля быстрых каналов параллельных МБКП предназначена для подключения к SBus-шине вычислительного комплекса (ВК) устройств специализированного вычислителя (СВ) изделия Л-01-ЦВК по быстрым параллельным каналам (БКП).

Ячейка модуля быстрых каналов параллельных МБКП предназначена для подключения к SBus-шине вычислительного комплекса (ВК) устройств специализированного вычислителя (СВ) изделия Л-01-ЦВК по быстрым параллельным каналам (БКП).

Ячейка модуля быстрых каналов параллельных МБКП предназначена для подключения к SBus-шине вычислительного комплекса (ВК) устройств специализированного вычислителя (СВ) изделия Л-01-ЦВК по быстрым параллельным каналам (БКП). Ячейка МБКП представляет собой однослотовую SВus-ячейку с двумя соединителями. Существует две реализации ячейки – МБКП1 и МБКП2. Внешний вид ячеек одинаков, имеются небольшие различия в логике работы и внутреннем устройстве ячеек.

| Параметр | Значение |

|---|---|

| Интерфейс | шина SBus |

| Скорость передачи данных, Мбайт/с | до 20 |

| Длина линии связи между МБКП и внешним абонентом (по экранированной витой паре), м | до 3 |

| Напряжение питания, В | 5 |

| Потребляемый ток, А | до 1 |

| Средняя наработка на отказ ВК, ч, не менее | 9000 |

| Группа исполнения | зависит от ВК |

| Потребляемая мощность, Вт | 5 |

| Диапазон рабочих температур внешних условий применения, °С | зависит от ВК |

| Год начала производства | 2005 |

Ячейка МБКП1 содержит два канальных адаптера – передающий и приёмный, а МБКП2 – два приёмных канальных адаптера. Каждый из адаптеров обеспечивает сопряжение ВК с внешним абонентом по отдельному каналу БКП в симплексном режиме. Обмен информацией через оба адаптера могут выполняются одновременно и независимо друг от друга. Каждый адаптер имеет два набора БКП: основной и резервный. Обмен информацией выполняется всегда по одному из наборов, который выбирается программным способом при начальной инициализации.

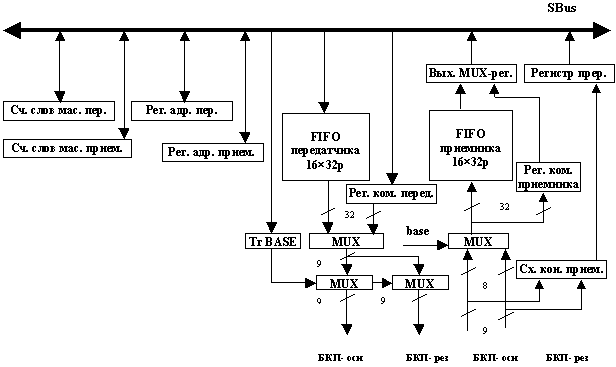

Основные составные части ячейки МБКП

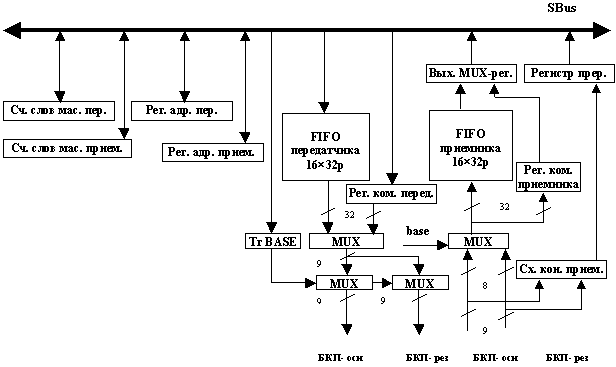

Структура ячейки МБКП1

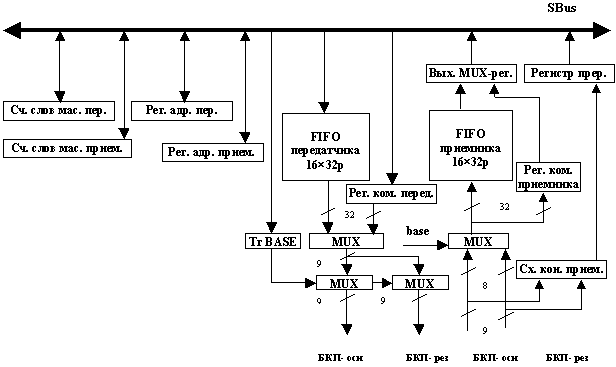

Структура ячейки МБКП2

Схемы управления и регистровая часть ячейки МБКП выполнены на ПЛИС типа EPF10K50SQC240-1 фирмы Altera. Для синхронизации обмена данная микросхема позволяет организовать внутреннюю оперативную память типа FIFO. Напряжение питания схем логики ПЛИС равно 2,5 В, а входных и выходных буферных схем – 3,3 В. Преобразование входного напряжения величиной 5 В в требуемые, выполнено на микросхемах MAX603CSA. Источниками и приёмниками канальных сигналов служат соответственно выходные и входные буфера ПЛИС.

Канал БКП совместим с каналом Link port микропроцессоров ADSP-2116x (Analog Devices Inc) и имеет побайтовый контроль передаваемой информации и дополнительный сигнал начальной установки (обнуления). Содержит 12 сигнальных линий:

Передача информации по каналу БКП производится 32-разрядными словами в виде 4-х байтовых посылок.

Поддерживается стандартный комплект программного обеспечения для платформы «Эльбрус».