Вычислительный модуль М1Э3МГ/C – двухпроцессорный высокопроизводительный вычислитель. Основной компонент вычислительных комплексов на микропроцессорах архитектуры «Эльбрус».

Вычислительный модуль М1Э3МГ/C – двухпроцессорный высокопроизводительный вычислитель. Основной компонент вычислительных комплексов на микропроцессорах архитектуры «Эльбрус».

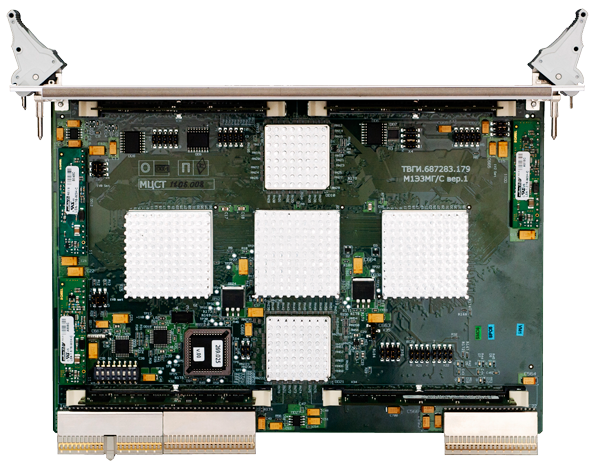

Вычислительный модуль М1Э3МГ/C – двухпроцессорный высокопроизводительный вычислитель. Основной компонент вычислительных комплексов на микропроцессорах архитектуры «Эльбрус».. Представляет собой ячейку в конструктиве cPCI типоразмера 6U. Устанавливается в объединительную панель крейта Compact PCI с помощью стандартных соединителей и занимает в нём два слота.

Основной элемент модуля – печатная плата с установленными на ней интегральными микросхемами, соединителями cPCI и передней панелью.

| Параметр | Значение |

|---|---|

| Микропроцессор | 2 × «Эльбрус» |

| Тактовая частота процессора, МГц. | 300 |

| Кэш команд процессора, Кбайт | 64 |

| Кэш данных процессора, Кбайт | 64 |

| Оперативная память, Гбайт | 4 |

| Кэш второго уровня процессора, Кбайт | 256 |

| Каналы ввода/вывода | Fast Ethernet, RS-232, USB, Video, Centronics, Audio. |

| Средняя наработка на отказ ВК, ч, не менее | 9000 |

| Группа исполнения | зависит от ВК |

| Потребляемая мощность, Вт | 6 |

| Диапазон рабочих температур внешних условий применения, °С | зависит от ВК |

| Год начала производства | 2010 |

-

В состав модуля М1Э3МГ/C входят:

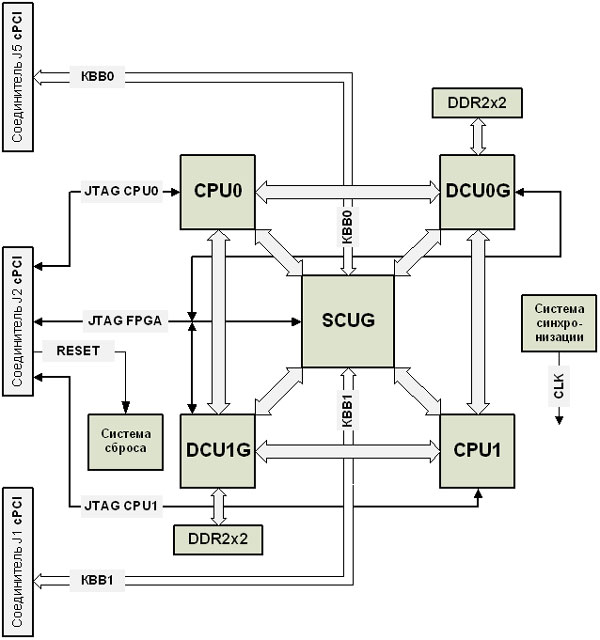

Структура модуля М1Э3МГ/C

Микропроцессоры «Эльбрус» (1891ВМ4Я) – основной узел модуля. Выполнены на основе архитектуры с широким командным словом VLIW. Отвечает за выполнение арифметических, логических операций и операций управления в машинных кодах.

Системный контроллер «северный мост» SCUG содержит в одной ПЛИС коммутатор адреса и контроллер ввода/вывода. SCUG со стороны центральной системы взаимодействует с адресным коммутатором и коммутатором данных. Интерфейс с адресным коммутатором служит для приёма и выдачи заявок на выполнение транзакций, интерфейс с коммутатором данных – обслуживает приём и выдачу данных.

Адресный коммутатор направляет заявки (адреса) от двух процессоров (CPU0 и CPU1) либо в контроллеры памяти для доступа к модулям оперативной памяти DDR2, либо в контроллер ввода/вывода SCUG для доступа к устройствам ввода-вывода. Кроме того, он проверяет наличие копий данных, к которым идут обращения, в кэш-памятях процессоров и реализует протокол когерентности, т.е. поддержки соответствия состояний этих копий друг другу и содержимому памяти.

Контроллер адресов запросов может направлять запросы в четыре независимых одноканальных контроллера памяти МС0, МС1, МС2, МС3, причём за один такт может выдаваться до двух запросов, один – в МС0 или МС2, находящиеся в одной микросхеме DCUG, и второй – в МС1 или МС3, находящиеся в другой микросхеме DCUG.

Коммутаторы данных и контроллеры памяти (DCUG) размещены в двух ПЛИС (DCU0G и DCU1G), по одному в каждой. Коммутаторы данных служат для передачи данных между процессорами CPU0, CPU1, контроллерами памяти МС и системным контроллером ввода/вывода SCUG. Два процессора получают и выдают данные через два DCUG, работающих синхронно и независимо. Каждый процессор имеет 128-разрядную шину приёма данных и 128-разрядную шину выдачи данных. Старшие 64 разряда обеих шин соединены с DCU1G, младшие – с DCU0G. Аналогичным образом устроена 64-разрядная шина данных для контроллера SCUG: старшие 32 разряда передаются через DCU1G, младшие 32 разряда – через DCU0G.

Единицей данных при обменах с процессорами является строка кэша, равная 64 байтам, из которых на каждый DCUG приходится по 32 байта. Старшие 32 байта кэш-строки каждого процессора проходят через DCU1G, а младшие – через DCU0G.

Обмен данными между контроллером SCUG и MC может производиться посылками меньше 32 байт. Выходной интерфейс от DCUG к процессорам, с I/O и канал запросов и разрешений от МC работают в DDR-режиме, поэтому эквивалентная ширина шины к процессорам равна 128, а к I/O – 32 разрядам соответственно. Все остальные интерфейсы – SDR. При тактовой частоте 100 МГц пропускная способность входов от CPU – 1,6 Гбайт/с, от I/O – 0,8 Гбайт/с, от MC к CPU – 3,2 Гбайт/с.

С контроллерами памяти МС каждый DCUG связан четырьмя 256-разрядными шинами для передачи в обоих направлениях.

Конфигурационные программируемые постоянные запоминающие устройства (ППЗУ) хранят конфигурационную информацию для контроллеров DCUG иSCUG.

Канал вода-вывода (КВВ) состоит из 10 параллельных дифференциальных полнодуплексных линков. Восемь линков предназначены для данных, один линк управления и один линк для передачи сигнала синхронизации. КВВ работает в двух основных режимах: BUS и DMA.

Режим BUS предназначен для работы с внешней периферией, например с контроллером ввода-вывода. Протокол, в этом случае, read-write и возможны размеры передаваемых данных в пакете – 1, 2, 4, 8, 16, 32, 64, 128, 256 байт.

Режим DMA предназначен для межмашинного обмена, например для объединения многопроцессорных модулей в многомашинную конфигурацию. Однако при этом для передачи возможны только размеры 4 байта и 256 байт.

Канал КВВ0 работает в BUS режиме и предназначен для взаимодействия с периферийным контроллером («южным мостом») E3SSB модуля МВ3S2/C. Канал КВВ1 работает в DMA режиме и предназначен для межмашинного обмена.

Поддерживается стандартный комплект программного обеспечения для платформы «Эльбрус».