Министерство образования и науки Российской Федерации Федеральное государственное автономное образовательное учреждение высшего профессионального образования «Московский физико-технический институт (государственный университет)»

# Разработка этапа планирования иерархии в маршруте иерархического проектирования

Студент 816 группы Трихин П. О. Научный руководитель: Терентьев Ю. И. Мальшин А. В.

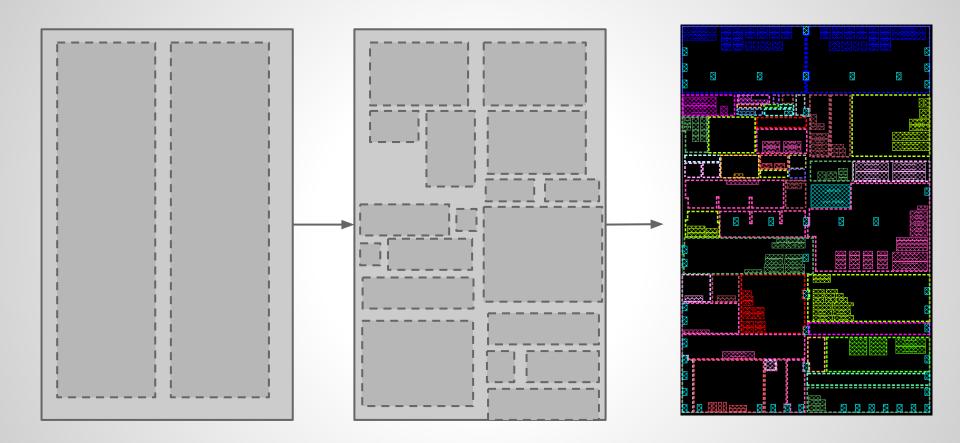

# Маршрут физического проектирования - последовательность действий, позволяющая из RTL описания получить физическую модель блока

Маршрут физического проектирования

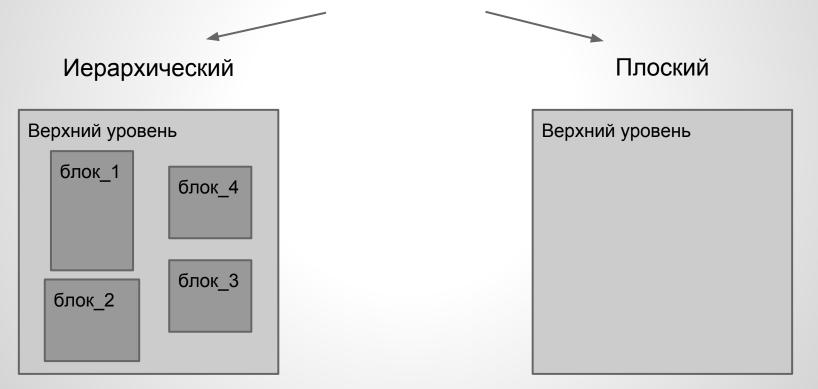

# Достоинства и недостатки плоского и иерархического подхода

#### Плоский

- Достоинства

- не требуется время для изучения иерархии блока

- Недостатки

- больше времени и вычислительных ресурсов для одной итерации проектирования

- неоптимальное размещение стандартных элементов

<u>Иерархический</u>

- Достоинства

- возможность распараллеливать проектирование блока

- о быстрое внесение изменений RTL

- Недостатки

- дополнительное время для изучения иерархии блока

## Цели работы:

- разработать маршрут иерархического проектирования

- Этап планирования иерархии

• спланировать иерархию блока p2\_gpu с использованием разработанного маршрута

провести анализ разработанного маршрута и его сравнение с плоским маршрутом

## Структура маршрута проектирования

Этап 1: планирование иерархии

Эта

Этап 2: проектирование блоков

Этап 3: проектирование верхнего уровня

- синтез

- планирование и размещение иерархии

- передача физических и временных ограничений в плоский маршрут для блоков

- синтез на готовых блоках

- размещение логики верхнего уровня

- трассировка верхнего уровня

### Этап 1

• Синтез

### Цели:

- сохранение логической иерархии

- уменьшение времени работы САПР

#### Решения:

настройка САПР (команды: uniqify, change\_names) использование САПР design explorer

### Этап 1

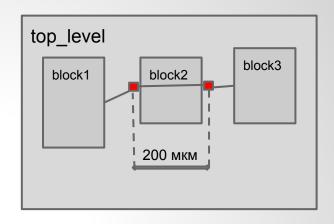

#### Проблемы размещения:

- разбиение на оптимальное число блоков

- размещение блоков на верхнем уровне

#### Решения:

- создание исходного размещения на основе изучения архитектуры и функциональности устройства

- оценка полученного размещения средствами САПР

create\_fp\_placement

optimize\_fp\_timing

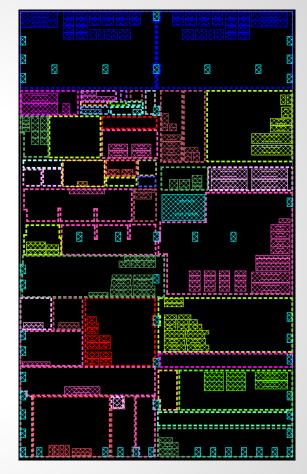

Верхний уровень р2\_gpu количество блоков - 51 штк

# **Этап 1 Этап 2**

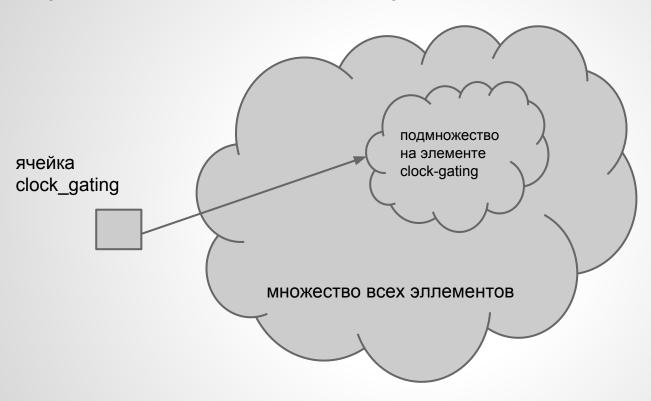

#### Передаваемая информация:

(floorplan)

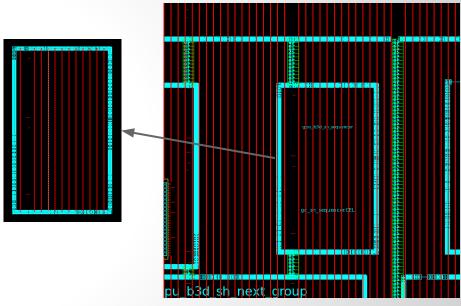

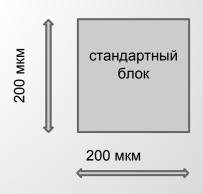

- геометрические размеры и форма блока

- расположение пинов (terminals)

- информация о задержках/емкостях на пинах (SDC)

- расположение макроблоков (soft\_macros)

- расположение вспомогательных элементов (tap\_cells, Power\_Switches, row, track)

- конфигурация сеток земли-питания и синхронизации

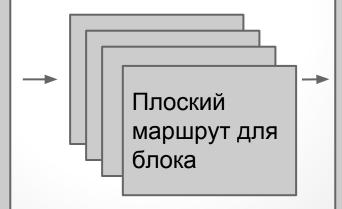

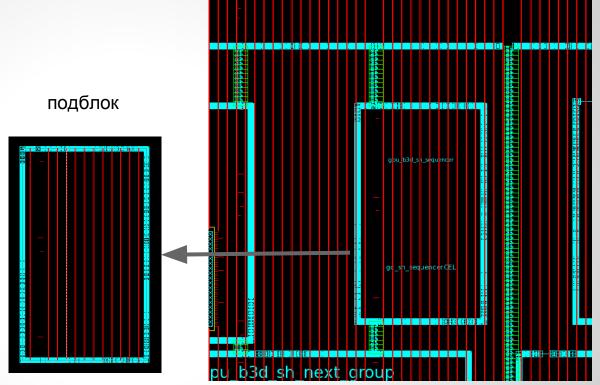

# Этап 2: плоский маршрут для блоков

Плоский маршрут детально проработан на предыдущих проектах. Необходимо было доработать его с учётом специфики иерархического маршрута

#### Особенности:

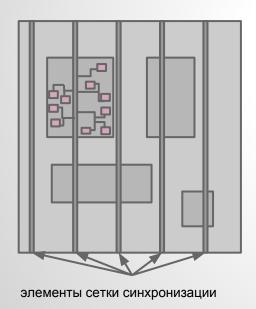

Совмещение сетки земли-питания Совмещение сетки синхронизации Отработка граничных эффектов размещения и трассировки.

Рис: передача сетки землипитания с целью дальнейшего совмещения на Этапе 3

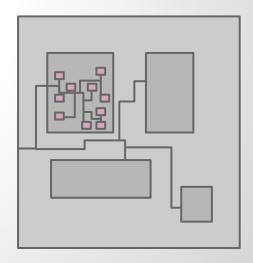

### Конструкция системы синхронизации

Построение системы синхронизации в общем случае

Построение системы синхронизации в частном случае блока p2\_gpu

- стандартный элемент

# Результаты

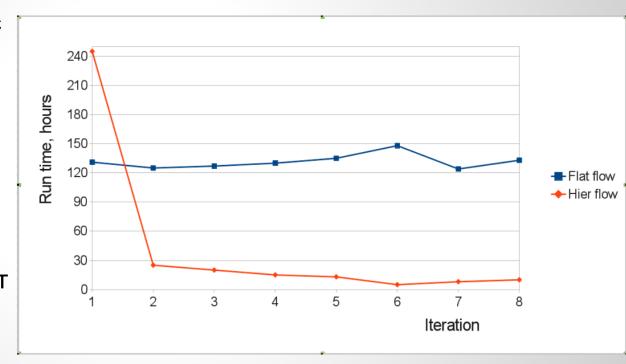

Сравнение маршрутов с точки зрения времени прохождения.

Вывод: после первой итерации (первого изменения RTL) - иерархический маршрут требует существенно меньше времени

Зависимость времени запуска от числа итераций.

# Результаты

Сравнение

утилизации блоков на этапе 1 и этапе 2 gc\_ra\_render gc\_ra\_output gc ra latencyFifo gc tx states rapper

gc\_tx\_ce\_lfifo

gc\_sh\_2core\_0

gc\_sh\_2core\_1 gc sh instruction

gc tx tc

gc\_sh\_cache\_top gc\_tx\_discard\_fifo

gc\_sh\_l1lstx\_request

gc\_tx\_cache\_complex\_3

gc sh local storage interface

gc\_pa

Название подблока

gc\_tx\_ta\_rapper\_FT gc\_tx\_filter\_FT\_top\_0

gc\_tx\_filter\_FT\_top\_1 gc\_tx\_L2\_formatter\_rapper

gc\_tx\_L2\_cache\_rapper\_sm

Uold -

утилизация на

верхнем урвоне

0,71 0,84 0,72 0,78 0.69 0,65 0,65 0,66 0.68 0,68 0,67

0,73

0.76

0,76

0,38

0,79

0,78

0,76

0,77

0,74

этапа

0,64 0,51 0,72 0,62 0,67 0,56 0,58 0,49 0,54

Unew - утилизация подблока после 2

0,58

0,83

0,67

0,67

0,68

0,42

0,63

0,68

0,66

0,74

0,64

Unew/Uold

0,82

0,76

0,71

0,93

0,91

1,04

0,86

0,88

0,72

0,80

1,24 0,92

0,89

0,89

1,09

0,81

0,87

0,88

0,96

0,86

# Спасибо за внимание!

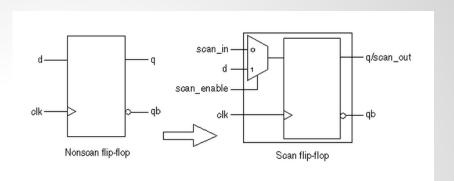

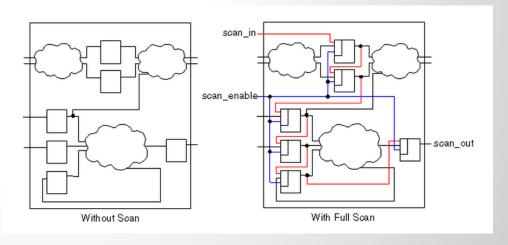

#### • Синтез

Для каждого подблока создаются 3\*N портов, где N - количество скан цепей в блоке.

Затем с использованием этих портов строятся скан-цепи

# Замена элементов при построении цепи

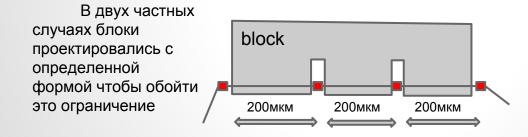

- буферизующая ячейка

Среднее расстояние между буферизующими ячейками - 200 мкм. Следовательно для разводимости на верхнем уровне размер подблока не должен превышать 200 мкм

#### Верхний уровень

Сетка земли-питания и расположение особых ячеек (tap, power switch) были скопированы в подблоки, для того чтобы при подстановке на верхний уровень все эти элементы были синхронизированы.

#### • Синтез

- Подгрузка флорплан файлов

- Подгрузка сетки земли питания

### Проблема системы синхронизации с блоком р2\_gpu