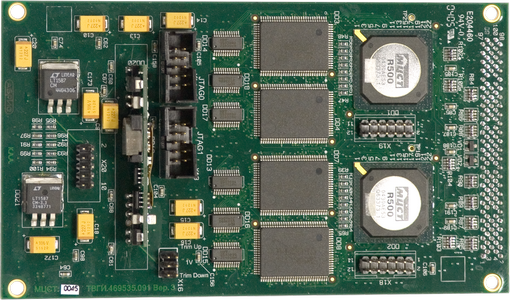

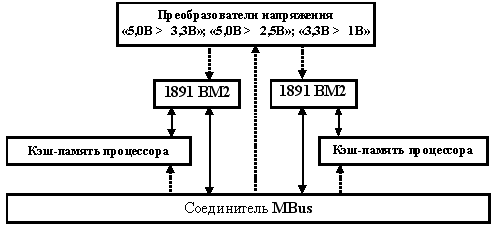

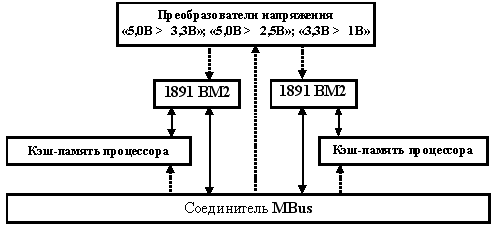

Структура ячейки МСР-1

Микропроцессор МЦСТ R500 (1891ВМ2) – основной узел ячейки. Выполнен на основе архитектуры с сокращённым набором команд – RISC. Отвечает за выполнение арифметических, логических операций и операций управления в машинных кодах. В микропроцессор встроен кэш-контроллер второго уровня, который выполняет следующие функции:

- управляет внешней кэш-памятью данных объёмом 4 Мбайт и внешней памятью тэгов;

- включает контроллер для копирования и заполнения блоков при размере блока равном КЭШ-строке;

- поддерживает многопроцессорную работу, обеспечивая КЭШ-когерентность (согласованность копий данных).

Кэш-память одного процессора реализована на двух микросхемах типа K7A163600A-QC25 фирмыSamsung ёмкостью 2 Мбайт каждая, ещё одна микросхема этого же типа используется для реализации памяти тэгов (384 Кбайт) микропроцессора.

Высокочастотный разъём MBus обеспечивает соединение с модулем МВ/С для совместной работы с ещё одной такой же ячейкой или с модулем MV/C для совместной работы с двумя микропроцессорами 1891ВМ2 модуля.